本文介绍一个基于Spirit_V4开发板、使用Quartus II软件设计与开发的高精度秒表倒计时器系统。该系统采用Verilog HDL硬件描述语言进行模块化设计,实现了秒表(正计时)、倒计时、暂停、复位等核心功能,精度可达0.01秒(10ms)。

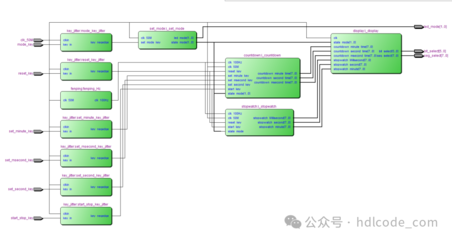

一、 系统总体架构

该系统采用自顶向下的设计方法,主要包含以下功能模块:

- 顶层模块 (top_timer):实例化并连接所有子模块,定义与开发板物理资源(时钟、按键、数码管、LED)的接口。

- 时钟分频与使能生成模块 (clk_gen):将板载50MHz主时钟进行分频,产生全局时序控制所需的10ms(100Hz)基准时钟使能信号,确保计时精度。

- 核心计时与控制模块 (timer_core):系统的核心状态机。根据按键输入,在“秒表模式”、“倒计时模式”、“暂停”、“复位”等状态间切换,并执行相应的计数逻辑。

- 按键消抖模块 (key_debounce):对机械按键产生的抖动信号进行滤波,确保每次按键只产生一个稳定的有效脉冲。

- 数码管动态扫描驱动模块 (seg_driver):将计时器产生的BCD码时间数据(时、分、秒、0.01秒)转换为七段数码管段选信号,并通过时分复用方式驱动多位数码管显示。

- LED指示模块 (led_indicator):根据系统当前工作模式(如运行、暂停、倒计时结束),控制LED灯给出直观的状态指示。

二、 关键模块Verilog代码设计要点

1. 时钟分频模块 (clk_gen)

module clk_gen(

input clk_50m, // 50MHz时钟

input rst_n, // 异步低电平复位

output reg clken10ms // 10ms使能脉冲

);

reg [19:0] cnt; // 50M / 100 = 500,000, 需要19位计数器

always @(posedge clk50m or negedge rstn) begin

if (!rst_n) begin

cnt <= 20'd0;

clken10ms <= 1'b0;

end

else begin

if (cnt == 20'd499_999) begin // 计数到499999,产生一个周期的高脉冲

cnt <= 20'd0;

clken10ms <= 1'b1;

end

else begin

cnt <= cnt + 1'b1;

clken10ms <= 1'b0;

end

end

end

endmodule2. 核心计时与控制模块 (timer_core) 状态机设计

该模块定义了三个主要状态:IDLE(复位/初始)、RUN(计时运行)、PAUSE(暂停)。在RUN状态下,根据模式选择信号mode(来自按键),决定是进行正计时累加还是倒计时递减。倒计时初值可通过预置寄存器设置,当倒计时减至零时,产生结束信号并触发LED警报。

3. 按键消抖模块 (key_debounce)

采用经典的计数器消抖法。当检测到按键电平变化后,启动一个约20ms的计时器,在此期间持续采样,若电平保持稳定,则输出有效的按键脉冲。这能有效滤除机械触点闭合/断开时产生的5-10ms抖动。

4. 数码管驱动模块 (seg_driver)

该模块将内部存储的24位时间数据(格式为:HH-MM-SS-MS,每4位为一个BCD码)按位分离,并通过一个高速扫描计数器(约1KHz)循环选中每一位数码管,同时输出对应的段码数据,利用人眼视觉暂留实现稳定显示。

三、 Quartus II工程开发流程

- 新建工程:指定工程目录、器件型号(对应Spirit_V4开发板上的FPGA,如Cyclone IV EP4CE10F17C8)。

- 设计输入:创建Verilog源文件,编写上述各模块代码。

- 分析与综合:Quartus对代码进行逻辑综合,生成门级网表。

- 引脚分配:根据Spirit_V4开发板原理图,将设计中的输入输出信号分配到具体的物理引脚(如时钟引脚、按键引脚、数码管段选/位选引脚、LED引脚)。这是硬件实现的关键一步。

- 全编译:执行完整的编译流程,包括综合、布局布线、时序分析和编程文件生成。

- 时序仿真(可选但推荐):使用ModelSim等工具进行功能仿真,验证计时精度、按键响应和状态切换逻辑的正确性。

- 板级调试与下载:通过USB-Blaster将生成的

.sof或.jic文件下载到Spirit_V4开发板中,进行实际功能测试。

四、 功能测试与性能分析

在实际测试中,系统应实现以下功能:

- 秒表模式:按下“开始/暂停”键开始正计时,再次按下暂停,可随时复位。

- 倒计时模式:通过模式键切换至倒计时,可预置时间(例如通过拨码开关或组合按键设定),启动后开始递减,归零时蜂鸣(或LED闪烁)报警。

- 高精度显示:稳定显示

00:00:00.00至99:59:59.99的时间范围。

系统精度主要由10ms使能信号的稳定性决定,该信号源于50MHz晶振,误差极小,完全满足常规高精度计时需求。

五、

本项目完整展示了使用Verilog HDL在FPGA平台上设计一个数字系统的流程。通过模块化设计、状态机控制、时钟管理、人机接口(按键、显示)驱动等技术的综合运用,成功在Spirit_V4开发板上实现了一个功能完善、性能稳定的高精度秒表倒计时器。该设计方法可进一步扩展,如增加多组计时存储、串口通信上位机控制等功能,具有良好的教学意义和实践价值。